您好!歡迎光臨烜芯微科技品牌官網(wǎng)!

- 收藏?zé)@芯微

- 手機(jī)訪問

掃一掃訪問手機(jī)網(wǎng)站 - 在線留言

- 網(wǎng)站地圖

傳真:

18923864027

QQ:

709211280

地址:

深圳市福田區(qū)振中路84號(hào)愛華科研樓7層

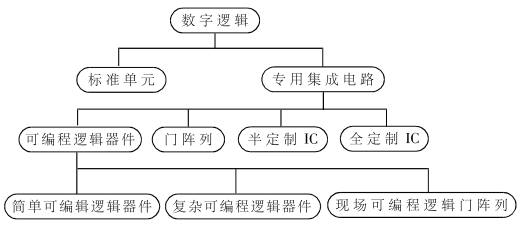

FPGA和CPLD的區(qū)別詳解FPGA是現(xiàn)場(chǎng)可編程邏輯門陣列的簡(jiǎn)稱,是電子設(shè)計(jì)的一個(gè)里程碑。CPLD是復(fù)雜可變成邏輯器件的簡(jiǎn)稱。雖然FPGA和CPLD都是可

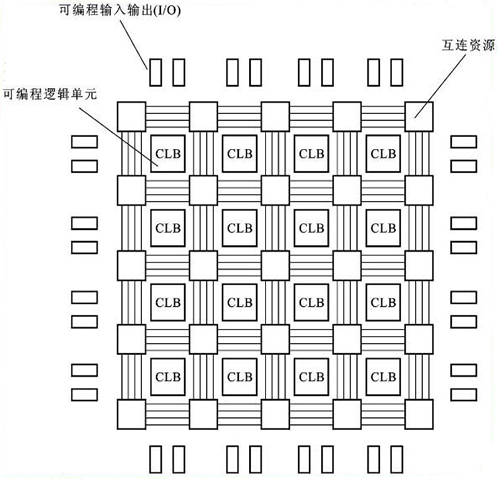

FPGA的基本結(jié)構(gòu)介紹FPGA 器件屬于專用集成電路中的一種半定制電路,是可編程的邏輯列陣,能夠有效的解決原有的器件門電路數(shù)較少的問題。FP

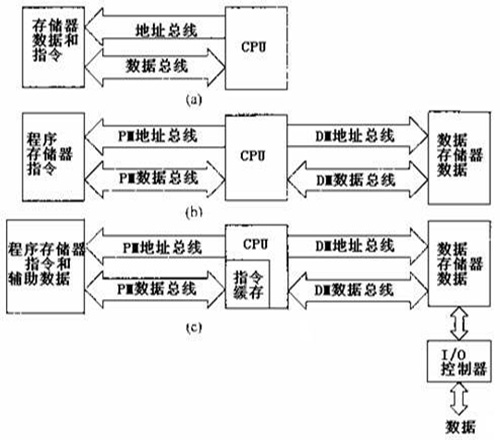

FPGA與單片機(jī)的區(qū)別介紹FPGA是在PAL、GAL、CPLD等可編程器件的基礎(chǔ)上進(jìn)一步發(fā)展的產(chǎn)物。它的出現(xiàn)的,既解決了定制電路的不足,又克服了原有

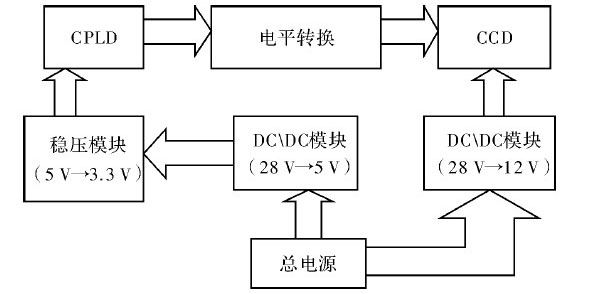

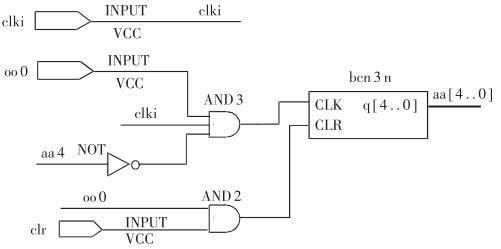

基于CPLD的線陣CCD驅(qū)動(dòng)電路設(shè)計(jì)圖解隨著半導(dǎo)體微電子技術(shù)的迅猛發(fā)展,如何實(shí)現(xiàn)高精度的運(yùn)動(dòng)裝置角度和位移測(cè)量,一直是系統(tǒng)或設(shè)備設(shè)計(jì)中需

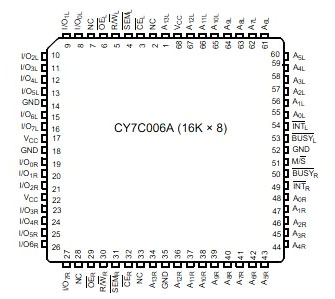

基于FPGA的雙口RAM設(shè)計(jì)介紹隨著電子技術(shù)的飛速發(fā)展,大容量、高速FPGA器件具有集成度高、體積小、靈活可重配置、實(shí)驗(yàn)風(fēng)險(xiǎn)小等優(yōu)點(diǎn),在復(fù)雜

CPLD實(shí)現(xiàn)數(shù)字濾波及抗干擾的設(shè)計(jì)圖解濾波和抗干擾是任何智能儀器系統(tǒng)都必須考慮的問題,在傳統(tǒng)的應(yīng)用系統(tǒng)中,濾波部分往往要占用較多的軟件

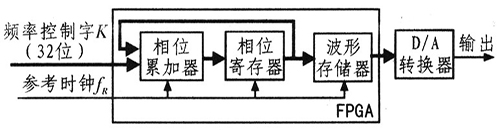

基于FPGA和DDS的信號(hào)源實(shí)現(xiàn)設(shè)計(jì)介紹DDS一般指DDS信號(hào)發(fā)生器,其采用直接數(shù)字頻率合成(Direct Digital Synthesis,簡(jiǎn)稱DDS)技術(shù),與第二代

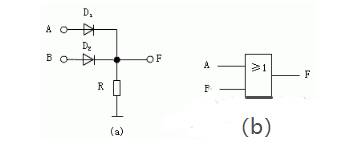

邏輯門的種類與電路圖介紹邏輯門主要使用二極管或晶體管作為電子開關(guān)來實(shí)現(xiàn),但也可以使用真空管、電磁繼電器(繼電器邏輯)、流體邏輯、氣動(dòng)

采用多種EDA工具的FPGA設(shè)計(jì)圖解如今,片上系統(tǒng)(SoC)技術(shù)的出現(xiàn)在數(shù)字系統(tǒng)設(shè)計(jì)引起變動(dòng);為適應(yīng)產(chǎn)品盡快上市的要求,設(shè)計(jì)者必須合理選擇各EDA

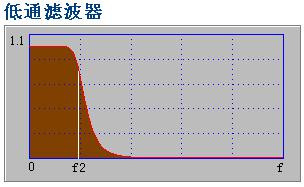

濾波器的原理和作用詳解濾波器是什么?濾波器是對(duì)波進(jìn)行過濾的器件,一般有兩個(gè)端口,一個(gè)輸入信號(hào)、一個(gè)輸出信號(hào)。可以說它是重要的電子元

濾波器的分類與特點(diǎn)圖解濾波器是一種選頻裝置,可以使信號(hào)中特定的頻率成分通過,而極大地衰減其它頻率成分。在測(cè)試裝置中,利用濾波器的這

電源濾波器的工作原理與作用介紹隨著電子設(shè)計(jì)、計(jì)算機(jī)與家用電器的大量涌現(xiàn)和廣泛普及,電網(wǎng)噪聲干擾日益嚴(yán)重并形成一種公害。特別是瞬態(tài)噪